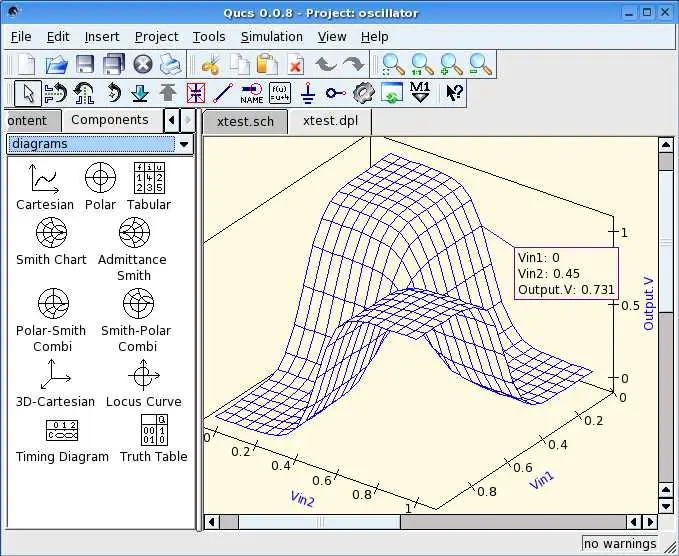

To illustrate the performance of this emerging GPL simulator a number of examples taken from DC to RF are described. This paper outlines the structure and simulation capabilities of the Qucs simulator. Recent improvements to the Qucs/ADMS interface now allow a well defined procedure for VerilogA model construction. These include, traditional subcircuits, equation defined devices and VerilogA compact models generated using the ADMS compiler. The package is equipped with a range of device and modeling features which allow fast prototyping of experimental compact device and circuit. Versions are available for most of the popular computer operating systems. It is one of the GPL simulators supporting VerilogA compact model standardization. Qucs is an open source circuit simulator with extensive device and circuit modeling capabilities. To illustrate the presented modeling techniques RF diode, BJT and MESFET macromodels are described and their Harmonic Balance performance simulated with Qucs and Xyce c. These form a class of compact macromodel that has improved Harmonic Balance simulation performance. The modeling of semiconductor devices centered on non-linear Equation-Defined Devices and blocks of Verilog-A code, combined with linear components, is introduced. The same comment also applies to a number of legacy compact semiconductor device models. guarantee that these will function without Harmonic Balance simulation convergence problems. Although Qucs supports conventional SPICE semiconductor device models, whose static current/voltage and dynamic charge characteristics exhibit second and higher order derivatives may not be continuous, there is no. This paper is concerned with the development and evaluation of a number of modeling techniques which improve Qucs Harmonic Balance simulation performance of RF compact device models.

To illustrate the properties and use of the Qucs Verilog-A module synthesiser, the text includes a number of semiconductor device modelling examples and in some cases compares their simulation performance with conventional behavioural device models. This paper introduces a new approach to the generation of Verilog-A compact device models from Qucs circuit schematics using a purpose built analogue module synthesizer.

In traditional circuit simulation, the generation of a Verilog-A model from a schematic, with embedded non-linear behavioural sources, is not automatic but is normally undertaken manually. Following, the standardization of Verilog-A, it has become a preferred hardware description language where analogue models are written in a netlist format combined with more general computer programming features for sequencing and controlling model operation. The Qucs equation-defined device is an extension of the SPICE style non-linear B type controlled source which adds dynamic charge properties to behavioural sources, allowing for example, voltage and current dependent capacitance to be easily modelled. modelling physical phenomena and system performance. The current generation of SPICE-based open source general public license circuit simulators, including Qucs, Ngspice and Xyce ©, implements a range of mathematical operators and functions for. Since the introduction of SPICE non-linear controlled voltage and current sources, they have become a central feature in the interactive development of behavioural device models and circuit macromodels. The paper also presents a number of examples which illustrate the capabilities of the Qucs model construction tools implemented by the Qucs development team.

This paper outlines recent advances in Qucs equation based modelling techniques, including (1) Qucs equation defined device/Verilog-A compatibility improvements, (2) non-linear radio frequency equation defined device modelling techniques, (3) modelling non-linear physical processes, and (4) methods for construction Verilog-A models for established and new technologies. packages supporting the MOS-AK Verilog-A standardisation initiative. The Qucs circuit simulator is one of the GPL software. The Verilog-A subset of the Verilog- AMS hardware description language being a popular choice of hardware description language for model construction. Advances in circuit simulation technology suggest a strong movement towards software packages which promote equation based compact semiconductor device model and circuit macromodel development.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed